### Data Sheet February 1998

# microelectronics group

# **T7503 Dual PCM Codec with Filters**

**Bell Labs Innovations**

### Features

- +5 V only

- Automatic powerdown mode

- Low-power, latch-up-free CMOS technology

- On-chip sample and hold, autozero, and precision voltage reference

- Differential architecture for high noise immunity and power supply rejection

- Automatic master clock frequency selection

- 2.048 MHz or 4.096 MHz fixed data rate

- Frame sync controlled channel swapping

- Differential analog I/O

- 300 Ω output drivers

- Operating temperature range: -40 °C to +85 °C

- µ-law companding

## **Applications**

- Speakerphone

- Telephone answering device (TAD)

**Lucent Technologies**

POTS for ISDN

# Description

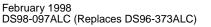

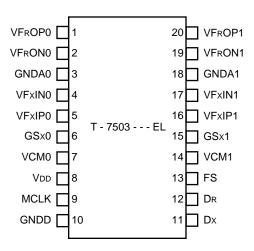

The T7503 device is a single-chip, two-channel  $\mu$ -law PCM codec with filters. This integrated circuit provides analog-to-digital and digital-to-analog conversion. It provides the transmit and receive filtering necessary to interface a voice telephone circuit to a time-division multiplexed (TDM) system. The device features a differential transmit amplifier, and the power receive amplifier is capable of driving 600  $\Omega$  differentially. PCM timing is defined by a single frame sync pulse. This device operates in a delayed timing mode (digital data is valid one clock cycle after frame sync goes high). The T7503 is packaged in a 20-pin SOJ.

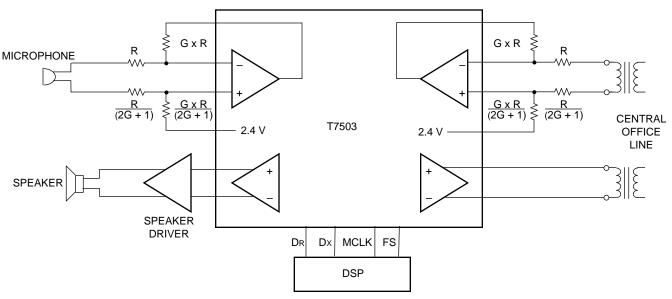

Figure 1. Block Diagram

# **Functional Description**

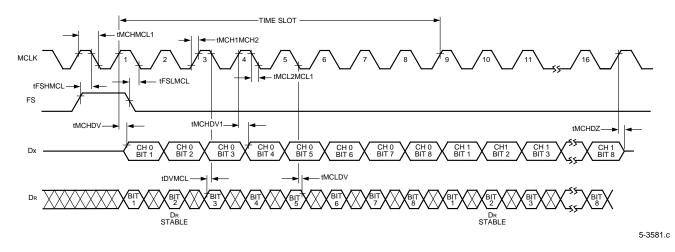

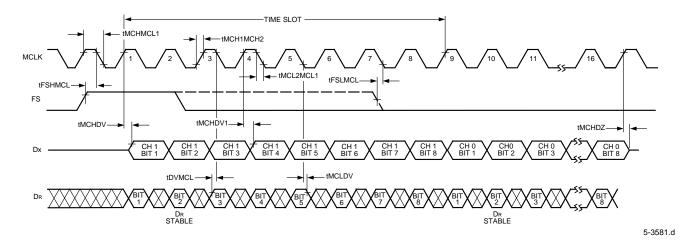

The T7503 has one frame sync (FS) input that determines transmit and receive data timing for both channels. The width of the FS pulse determines the order of the two channels on the PCM buses. If FS is nominally one MCLK period wide (see Figure 5), the data for channel 0 is first. If FS is nominally two or more MCLK periods wide (Figure 6), the data for channel 1 is first. During a single  $125 \,\mu$ s frame, the frame sync input is supplied a single pulse.

The frequency of the master clock must be either 2.048 MHz or 4.096 MHz. Internal circuitry determines the master clock frequency during the powerup reset interval.

Powerdown is achieved by removing the FS pulse for at least 500 µs with MCLK active, after which MCLK may be removed. Both channels are powered down together. Powerdown is not guaranteed if MCLK is lost, unless the device is already in the powerdown mode.

5-3787

# **Pin Information**

5-3788

# Pin Information (continued)

### Table 1. Pin Descriptions

| Symbol           | Pin     | Туре | Name/Function                                                                                                                                                                                                                                                                                         |

|------------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VFxIN1<br>VFxIN0 | 17<br>4 | I    | Voice Frequency Transmitter Negative Input. Analog inverting input to the uncommitted operational amplifier at the transmit filter input.                                                                                                                                                             |

| VFxIP1<br>VFxIP0 | 16<br>5 | I    | Voice Frequency Transmitter Positive Input. Analog noninverting input to the uncommitted operational amplifier at the transmit filter input.                                                                                                                                                          |

| GSx1<br>GSx0     | 15<br>6 | 0    | <b>Gain Set for Transmitter.</b> Output of the transmit uncommitted operational amplifier. The pin is the input to the transmit differential filters.                                                                                                                                                 |

| VFROP1<br>VFROP0 | 20<br>1 | 0    | Voice Frequency Receiver Positive Output. This pin can drive $300 \Omega$ (or greater) loads.                                                                                                                                                                                                         |

| VFrON1<br>VFrON0 | 19<br>2 | 0    | Voice Frequency Receiver Negative Output. This pin can drive 300 $\Omega$ (or greater) loads.                                                                                                                                                                                                         |

| Vdd              | 8       | _    | +5 V Power Supply. This pin should be bypassed to analog ground with at least 0.1 $\mu$ F of capacitance as close to the device as possible. VDD serves both analog and digital internal circuits.                                                                                                    |

| GNDA1<br>GNDA0   | 18<br>3 |      | <b>Analog Grounds</b> . Both ground pins must be connected on the circuit board. AGND serves both analog and digital internal circuits.                                                                                                                                                               |

| Dr               | 12      | I    | <b>Receive PCM Data Input</b> . The data on this pin is shifted into the device on the fall-<br>ing edges of MCLK. Sixteen consecutive bits of data (8 bits for channel 0, and<br>8 bits for channel 1) are entered after the FS pulse has been detected.                                             |

| Dx               | 11      | 0    | <b>Transmit PCM Data Output</b> . This pin remains in the high-impedance state except during active transmit time slots. Sixteen consecutive bits of data (8 bits for channel 0 and 8 bits for channel 1) are shifted out on the rising edge of MCLK. Data is shifted out on the rising edge of MCLK. |

| MCLK             | 9       | I    | <b>Master Clock Input</b> . The frequency must be 2.048 MHz or 4.096 MHz. This clock serves as the bit clock for all PCM data transfer. A 40% to 60% duty cycle is required.                                                                                                                          |

| GNDD             | 10      | —    | Digital Ground. Ground connection for the digital circuitry.                                                                                                                                                                                                                                          |

| FS               | 13      | lq*  | <b>Frame Sync</b> . This signal is an edge trigger and must be high for a minimum of one MCLK cycle. This signal must be derived from MCLK. If FS is low for 500 $\mu$ s while MCLK remains active, then the device fully powers down. An internal pull-down device is included on FS.                |

| VCM0<br>VCM1     | 7<br>14 | 0    | Voltage Common Mode. 2.4 Vdc.                                                                                                                                                                                                                                                                         |

\* I<sup>d</sup> indicates a pull-down device is included on this lead.

## **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of this data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

| Parameter                                 | Symbol | Min  | Max       | Unit |

|-------------------------------------------|--------|------|-----------|------|

| Storage Temperature Range                 | Tstg   | -55  | 150       | °C   |

| Power Supply Voltage                      | Vdd    |      | 6.5       | V    |

| Voltage on Any Pin with Respect to Ground | —      | -0.5 | 0.5 + Vdd | V    |

| Maximum Power Dissipation (package limit) | PD     | _    | 600       | mW   |

# **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. Lucent Technologies Microelectronics Group employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used to define the model. No industry-wide standard has been adopted for CDM. However, a standard HBM (resistance =  $1500 \Omega$ , capacitance = 100 pF) is widely used and therefore can be used for comparison purposes. The HBM ESD threshold presented here was obtained by using these circuit parameters:

| HBM ESD Threshold Voltage |         |  |  |  |  |

|---------------------------|---------|--|--|--|--|

| Device                    | Rating  |  |  |  |  |

| T7503                     | >2000 V |  |  |  |  |

# **Electrical Characteristics**

Specifications apply for T<sub>A</sub> = -40 °C to +85 °C, V<sub>DD</sub> = 5 V  $\pm$  5%, MCLK = either 2.048 MHz or 4.096 MHz, and GND = 0 V, unless otherwise noted.

### dc Characteristics

#### Table 2. Digital Interface

| Parameter                                | Symbol | Test Conditions                   | Min | Тур   | Max | Unit |

|------------------------------------------|--------|-----------------------------------|-----|-------|-----|------|

| Input Low Voltage                        | Vil    | All digital inputs                | _   | —     | 0.8 | V    |

| Input High Voltage                       | Vін    | All digital inputs                | 2.0 | —     | —   | V    |

| Output Low Voltage                       | Vol    | Dx, IL = 3.2 mA                   | _   | —     | 0.4 | V    |

| Output High Voltage                      | Vон    | Dx, I∟ = −3.2 mA                  | 2.4 | —     | _   | V    |

|                                          |        | Dx, I∟ = −320 μA                  | 3.5 | —     | —   | V    |

| Input Current Pins Without Pull-<br>down | lı     | Any digital input GND < VIN < VDD | -10 | ±0.01 | 10  | μA   |

| Input Current Pin with Pull-down         | lı     | Any digital input GND < VIN < VDD | 2   | 10    | 150 | μA   |

| Output Current in High-impedance State   | loz    | Dx                                | -30 | ±0.02 | 30  | μA   |

| Input Capacitance                        | Сі     |                                   | _   |       | 5   | pF   |

# Electrical Characteristics (continued)

### dc Characteristics (continued)

#### Table 3. Power Dissipation

Power measurements are made at MCLK = 4.096 MHz, outputs unloaded.

| Parameter         | Symbol | Test Conditions                  | Min | Тур | Max | Unit |

|-------------------|--------|----------------------------------|-----|-----|-----|------|

| Powerdown Current | Iddo   | MCLK present and FS $\leq$ 0.4 V | _   | 0.1 | 1   | mA   |

| Powerup Current   | Iddu   | MCLK, FS pulse present           | _   | 18  | 25  | mA   |

## **Transmission Characteristics**

#### Table 4. Analog Interface

| Parameter                                                    | Symbol | Test Conditions                                          | Min  | Тур   | Max        | Unit  |

|--------------------------------------------------------------|--------|----------------------------------------------------------|------|-------|------------|-------|

| Input Resistance, FSxI                                       | Rvfxi  | VFxI = 2.4 V                                             | 1.0  | —     | —          | MΩ    |

| Input Leakage Current, VFxI                                  | BVFXI  | VFxI = 2.4 V                                             | -2.4 | ±0.01 | 2.4        | μA    |

| Input Capacitance, VFxIN, VFxIP                              | —      | —                                                        |      |       | 10         | pF    |

| Input Offset Voltage of Uncommitted<br>Op Amp, VFxIN – VFxIP | —      | _                                                        | -5   |       | 5          | mV    |

| Input Common-mode Voltage Range,<br>VFxIN, VFxIP             | _      | _                                                        | 1.2  |       | Vdd - 1.75 | V     |

| Input Common-mode Rejection Ratio,<br>VFxIN, VFxIP           | _      | _                                                        | —    | 60    |            | dB    |

| Gain Bandwidth Product (10 kHz) of Un-<br>committed Op Amp   | —      | _                                                        | —    | 3000  |            | kHz   |

| Equivalent Input Noise Between VFxIN<br>and VFxIP at GSx     | _      | _                                                        | —    | -30   |            | dBrnC |

| Output Voltage Range, GSx                                    | —      | —                                                        | 0.5  | —     | Vdd - 0.5  | V     |

| dc Open-loop Voltage Gain, GSx                               | Avol   | —                                                        | 90   | —     | —          | dB    |

| Differential Output dc Offset Voltage                        | —      | _                                                        | -80  | ±10   | 80         | mV    |

| Load Capacitance, GSx                                        | CLx1   | —                                                        | _    |       | 50         | pF    |

| Load Resistance, GSx                                         | RLx1   | —                                                        | 10   |       | —          | kΩ    |

| VCM Output Voltage Referenced to GND                         | —      | —                                                        | 2.25 | 2.35  | 2.5        | V     |

| VCM Output Load Capacitance                                  | —      | —                                                        | 0    | —     | 50         | pF    |

| Load Resistance, Vсм                                         | RLvсм  | —                                                        | 10   | —     | —          | kΩ    |

| Load Resistance, VFRO                                        | RLvfro | —                                                        | 300  | —     | —          | Ω     |

| Load Capacitance, VFRO                                       | CLVFRO | _                                                        | —    | _     | 100        | pF    |

| Output Resistance, VFRO                                      | ROvfro | 0 dBm0, 1020 Hz PCM code applied to DR                   |      | 0.3   | 3          | Ω     |

| Output Voltage, VFRO                                         | VOr    | Alternating $\pm$ zero $\mu$ -law PCM code applied to Dr | 2.25 | 2.35  | 2.5        | V     |

| Output Leakage Current, VFRO, Power-<br>down                 | IOvfro | —                                                        | -30  | ±0.02 | 30         | μA    |

| Output Voltage Swing, VFRO                                   | Vswr   | RL = 300 Ω                                               | 3.2  |       | —          | Vp-p  |

### ac Transmission Characteristics

Unless otherwise noted, the analog input is a 0 dBm0, 1020 Hz sine wave; the input amplifier is set for unity gain. The digital input is a PCM bit stream equivalent to that obtained by passing a 0 dBm0, 1020 Hz sine wave through an ideal encoder. The output level is sin(x)/x-corrected.

#### Table 5. Absolute Gain

| Parameter                                                  | Symbol | Test Conditions                                                                                         | Min   | Тур | Max  | Unit |

|------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------|-------|-----|------|------|

| Encoder Milliwatt<br>Response (transmit gain<br>tolerance) | EmW    | Signal input of 0.775 Vrms $\mu$ -law                                                                   | -0.25 |     | 0.25 | dBm0 |

| Decoder Milliwatt<br>Response (receive gain<br>tolerance)  | DmW    | Measured single-ended relative to 0.775 Vrms $\mu$ -law, PCM input of 0 dBm0 1020 Hz RL = 10 k $\Omega$ | -0.25 |     | 0.25 | dBm0 |

#### Table 6. Gain Tracking

| Parameter                                        | Symbol | Test Conditions                             | Min            | Тур | Max          | Unit     |

|--------------------------------------------------|--------|---------------------------------------------|----------------|-----|--------------|----------|

| Transmit Gain Tracking Error<br>Sinusoidal Input | GTx    | +3 dBm0 to –37 dBm0<br>–37 dBm0 to –50 dBm0 | -0.25<br>-0.50 | _   | 0.25<br>0.50 | dB<br>dB |

| Receive Gain Tracking Error<br>Sinusoidal Input  | GTr    | +3 dBm0 to –37 dBm0<br>–37 dBm0 to –50 dBm0 | -0.25<br>-0.50 |     | 0.25<br>0.50 | dB<br>dB |

#### **Table 7. Distortion**

| Parameter                                | Symbol | Test Conditions                                                                     | Min | Тур | Max | Unit |

|------------------------------------------|--------|-------------------------------------------------------------------------------------|-----|-----|-----|------|

| Transmit Signal to Distortion            | SDx    | $\mu$ -law +3 dBm0 $\leq$ VFxI $\leq$ -30 dBm0                                      | 36  |     |     | dB   |

|                                          |        | $\mu$ -law –30 dBm0 $\leq$ VFxI $\leq$ –40 dBm0                                     | 30  | —   | _   | dB   |

|                                          |        | $\mu$ -law –40 dBm0 $\leq$ VFxI $\leq$ –45 dBm0                                     | 25  |     |     | dB   |

| Receive Signal to Distortion             | SDr    | $\mu$ -law +3 dBm0 $\leq$ VFrO $\leq$ -30 dBm0                                      | 36  |     |     | dB   |

|                                          |        | $\mu$ -law –30 dBm0 $\leq$ VFRO $\leq$ –40 dBm0                                     | 30  | —   | _   | dB   |

|                                          |        | $\mu$ -law –40 dBm0 $\leq$ VFRO $\leq$ –45 dBm0                                     | 25  | —   | —   | dB   |

| Single Frequency Distortion,<br>Transmit | SFDx   | 200 Hz—3400 Hz, 0 dBm0 input,<br>output any other single<br>frequency ≤ 3400 Hz     | _   |     | -38 | dBm0 |

| Single Frequency Distortion,<br>Receive  | SFDr   | 200 Hz—3400 Hz, 0 dBm0 input,<br>output any other single<br>frequency ≤ 3400 Hz     | _   |     | -40 | dBm0 |

| Intermodulation Distortion               | IMD    | Transmit or receive, two frequencies<br>in the range (300 Hz—3400 Hz)<br>at –6 dBm0 | —   |     | -42 | dBm0 |

### ac Transmission Characteristics (continued)

#### **Table 8. Envelope Delay Distortion**

| Parameter                     | Symbol | Test Conditions                         | Min | Тур | Max | Unit |

|-------------------------------|--------|-----------------------------------------|-----|-----|-----|------|

| Tx Delay, Absolute            | Dxa    | f = 1600 Hz                             | _   | _   | 230 | μs   |

| Tx Delay, Relative to 1600 Hz | Dxr    | f = 500 Hz—600 Hz                       |     |     | 220 | μs   |

|                               |        | f = 600 Hz—800 Hz                       | —   | —   | 145 | μs   |

|                               |        | f = 800 Hz—1000 Hz                      | —   |     | 75  | μs   |

|                               |        | f = 1000 Hz—1600 Hz                     | —   |     | 40  | μs   |

|                               |        | f = 1600 Hz—2600 Hz                     |     |     | 75  | μs   |

|                               |        | f = 2600 Hz—2800 Hz                     | —   |     | 105 | μs   |

|                               |        | f = 2800 Hz—3000 Hz                     | —   | —   | 155 | μs   |

| Rx Delay, Absolute            | Dra    | f = 1600 Hz                             | _   | _   | 275 | μs   |

| Rx Delay, Relative to 1600 Hz | Drr    | f = 500 Hz—1000 Hz                      | -40 | _   | _   | μs   |

|                               |        | f = 1000 Hz—1600 Hz                     | -30 | —   | —   | μs   |

|                               |        | f = 1600 Hz—2600 Hz                     | _   | —   | 90  | μs   |

|                               |        | f = 2600 Hz—2800 Hz                     | —   |     | 125 | μs   |

|                               |        | f = 2800 Hz—3000 Hz                     |     | —   | 175 | μs   |

| Round Trip Delay, Absolute    | Drta   | With or between channels<br>f = 1600 Hz |     |     | 470 | μs   |

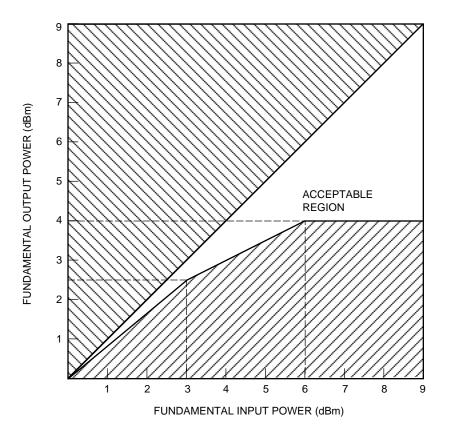

#### **Overload Compression**

Figure 4 shows the region of operation for encoder signal levels above the reference input power (0 dBm0).

**Figure 4. Overload Compression**

5-3586

### ac Transmission Characteristics (continued)

#### Table 9. Noise

| Parameter                                                 | Parameter Symbol Test Conditions |                                                                                                                                                          | Min            | Тур | Max               | Unit           |

|-----------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|-------------------|----------------|

| Transmit Noise                                            | Nxc                              |                                                                                                                                                          | —              | 13  | 18                | dBrnC0         |

| μ-Law                                                     |                                  | Input amplifier gain = 36 dB                                                                                                                             | —              | 16  | 19                | dBrnC0         |

| Receive Noise<br>μ-Law                                    | Nrc                              | PCM code is alternating positive and negative zero.                                                                                                      | _              | 6   | 13                | dBrnC0         |

| Noise, Single Frequency                                   | Nrs                              | f = 0  kHz—100 kHz,<br>VFxIN = 0 Vrms, measurement at<br>VFRO, DR = Dx                                                                                   |                |     | -53               | dBm0           |

| Power Supply Rejection Transmit                           | PSRx                             | V <sub>DD</sub> = 5.0 Vdc + 100 mVrms:<br>f = 0 kHz—4 kHz<br>f = 4 kHz—50 kHz                                                                            | 36<br>30       |     | _                 | dB<br>dB       |

| Power Supply Rejection Receive                            | PSRx                             | PCM code is positive one LSB.<br>$V_{DD} = 5.0 \text{ Vdc} + 100 \text{ mVrms}:$<br>f = 0  kHz - 4  kHz<br>f = 4  kHz - 25  kHz<br>f = 25  kHz - 50  kHz | 36<br>40<br>30 |     |                   | dB<br>dB<br>dB |

| Spurious Out-of-Band Signals at<br>VFRO Relative to Input | SOS                              | 0 dBm0, 300 Hz—3400 Hz input<br>PCM code applied:<br>4600 Hz—7600 Hz<br>7600 Hz—8400 Hz<br>8400 Hz—50 kHz                                                |                |     | -30<br>-40<br>-30 | dB<br>dB<br>dB |

#### Table 10. Receive Gain Relative to Gain at 1.02 kHz

| Frequency (Hz) | Min    | Тур    | Max    | Unit |

|----------------|--------|--------|--------|------|

| Below 3000     | -0.150 | ±0.04  | 0.150  | dB   |

| 3140           | -0.570 | ±0.04  | 0.150  | dB   |

| 3380           | -0.735 | -0.50  | 0.010  | dB   |

| 3860           | _      | -10.70 | -9.400 | dB   |

| 4600 and above |        |        | -28    | dB   |

#### Table 11. Transmit Gain Relative to Gain at 1.02 kHz

| Frequency (Hz) | Min    | Тур    | Max    | Unit |

|----------------|--------|--------|--------|------|

| 16.67          | _      | -50    | -30    | dB   |

| 40             | —      | -34    | -26    | dB   |

| 50             |        | -36    | -30    | dB   |

| 60             | —      | -50    | -30    | dB   |

| 200            | -1.800 | -0.5   | 0      | dB   |

| 300 to 3000    | -0.150 | ±0.04  | 0.150  | dB   |

| 3140           | -0.570 | ±0.04  | 0.150  | dB   |

| 3380           | -0.735 | -0.50  | 0.010  | dB   |

| 3860           | —      | -10.70 | -9.400 | dB   |

| 4600 and above | —      | —      | -32    | dB   |

#### ac Transmission Characteristics (continued)

#### Table 12. Interchannel Crosstalk (Between Channels) RF = $\leq$ 400 k $\Omega^*$

| Parameter                                                        | Symbol  | Test Conditions                                                                                                            | Min | Тур | Max | Unit |

|------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Transmit to Receive<br>Crosstalk 0 dBm0<br>Transmit Levels       | CTxx-ry | f = 300 Hz—3400 Hz<br>idle PCM code for channel under test;<br>0 dBm0 into any other single-channel VFxIN                  | _   |     | -75 | dB   |

| Receive to Transmit<br>Crosstalk 0 dBm0<br>Receive Levels        | CTrx-xy | f = 300 Hz—3400 Hz<br>VFxIN = 0 Vrms for channel under test;<br>0 dBm0 code level on any other single-channel DR           | _   |     | -75 | dB   |

| Transmit to Trans-<br>mit Crosstalk<br>0 dBm0 Transmit<br>Levels | СТхх-хү | f = 300 Hz—3400 Hz<br>0 dBm0 applied to any single-channel<br>VFxIN except channel under test,<br>which has VFxIN = 0 Vrms |     |     | -75 | dB   |

| Receive to Receive<br>Crosstalk 0 dBm0<br>Receive Levels         | CTrx-ry | f = 300 Hz—3400 Hz<br>0 dBm0 code level on any single-channel DR except<br>channel under test which has idle code applied  |     |     | -75 | dB   |

\* For Table 12, crosstalk into the transmit channels (VFxIN) can be significantly affected by parasitic capacitive feeds from GSx and VFRO outputs. PWB layouts should be arranged to keep these parasitics low. The resistor value of RF (from GSx to VFxIN) should also be kept as low as possible (while maintaining the load on GSx above 10 kΩ per Table 4) to minimize crosstalk.

#### Table 13. Intrachannel Crosstalk (Within Channels) RF = $\leq$ 400 k $\Omega^*$

| Parameter                                                  | Symbol  | Test Conditions                                                                         |  | Тур | Max | Unit |

|------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------|--|-----|-----|------|

| Transmit to Receive<br>Crosstalk 0 dBm0<br>Transmit Levels | CTxx-rx | f = 300 Hz—3400 Hz<br>idle PCM code for channel under test;<br>0 dBm0 into VFxIN        |  |     | -65 | dB   |

| Receive to Transmit<br>Crosstalk 0 dBm0<br>Receive Levels  | CTrx-xx | f = 300 Hz—3400 Hz<br>VFxIN = 0 Vrms for channel under test;<br>0 dBm0 code level on DR |  |     | -65 | dB   |

\* For Table 13, crosstalk into the transmit channels (VFxIN) can be significantly affected by parasitic capacitive feeds from GSx and VFRO outputs. PWB layouts should be arranged to keep these parasitics low. The resistor value of RF (from GSx to VFxIN) should also be kept as low as possible (while maintaining the load on GSx above 10 kΩ per Table 4) to minimize crosstalk.

# **Timing Characteristics**

| Symbol                 | Parameter                   | Test Conditions | Min | Тур | Max | Unit |

|------------------------|-----------------------------|-----------------|-----|-----|-----|------|

| tMCHMCL1               | Clock Pulse Width           |                 | 97  |     | _   | ns   |

| tCDC                   | Duty Cycle, MC              |                 | 40  |     | 60  | %    |

| tMCH1MCH2<br>tMCL2MCL1 | Clock Rise and<br>Fall Time | —               | 0   |     | 15  | ns   |

### Table 14. Clock Section (See Figures 5 and 6.)

### Table 15. Transmit Section (See Figures 5 and 6.)

| Symbol  | Parameter                | Test Conditions    | Min | Тур | Max | Unit |

|---------|--------------------------|--------------------|-----|-----|-----|------|

| tMCHDV  | Data Enabled on TS Entry | 0 < CLOAD < 100 pF | 0   | _   | 60  | ns   |

| tMCHDV1 | Data Delay from MC       | 0 < CLOAD < 100 pF | 0   | _   | 60  | ns   |

| tMCHDZ* | Data Float on TS Exit    | CLOAD = 0          | 10  | _   | 100 | ns   |

| tFSHMCL | Frame-sync Hold Time     | _                  | 50  | _   | _   | ns   |

| tMCLFSH | Frame-sync High Setup    | _                  | 50  | _   | —   | ns   |

| tFSLMCL | Frame-sync Low Setup     | _                  | 50  | _   | _   | ns   |

\* Timing parameter tMCHDZ is referenced to a high-impedance state.

#### Table 16. Receive Section (See Figures 5 and 6.)

| Symbol | Parameter          | Test Conditions | Min | Тур | Max | Unit |

|--------|--------------------|-----------------|-----|-----|-----|------|

| tDVMCL | Receive Data Setup |                 | 30  |     | _   | ns   |

| tMCLDV | Receive Data Hold  |                 | 15  |     |     | ns   |

## Timing Characteristics (continued)

Figure 5. Short FS Transmit and Receive Timing (Channel 0 First)

Figure 6. Long FS Transmit and Receive Timing (Channel 1 First)

# Applications

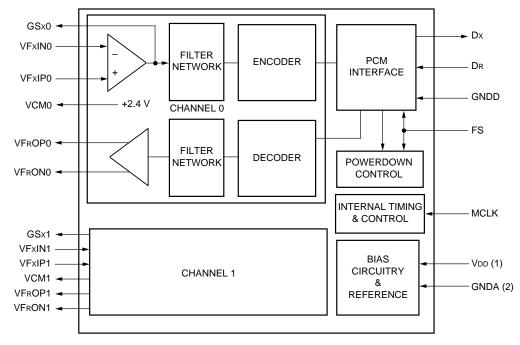

Figure 7 shows one possible analog connection. Fully differential structures used for the inputs minimize the noise gain from the internal 2.4 V bias voltage to the output of the single-ended transmitter op amp. The forward path gain is G, and by using resistors on the positive side that are a factor of 1/(2G + 1) of those on the negative side, the microphone and transformer feeds are kept well balanced. Using this ratio, G can be as low as unity (0 dB) without exceeding the common-mode limit of the op amp.

Users have wide latitude when selecting between a balanced amplifier configuration or a single-ended configuration. Single-ended configurations usually need fewer external components (e.g.,  $R_{IP} = \infty$  and  $R_{FP} = 0$  in Figure 2) but have two disadvantages: one, dc blocking from the source is typically required; two, internally generated noise at the common-mode pin VCM0 or VCM1 is amplified by G. For G > 10 (20 dB), this noise gain can become the factor that could limit performance. Single-ended configurations can be used even with microphones and transformers ( $R_{IP} = 0$  in these cases), but parasitic issues become somewhat more complex; so single-ended configurations are only suggested for gains of four (12 dB) or less.

5-3789.a

Figure 7. Typical T7503 Application

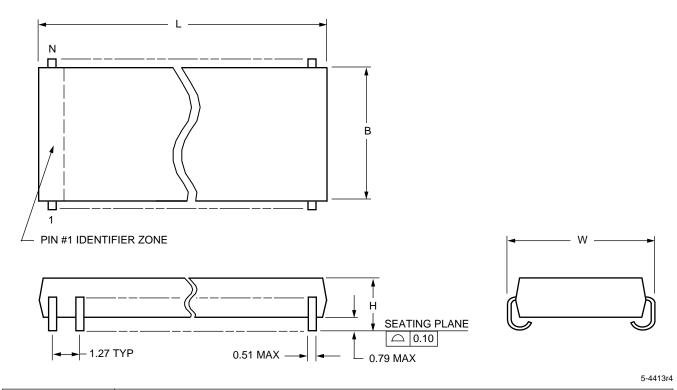

# **Outline Diagram**

Controlling dimensions are in inches.

|                                | Package Dimensions       |                          |                                       |                                         |                                      |  |  |

|--------------------------------|--------------------------|--------------------------|---------------------------------------|-----------------------------------------|--------------------------------------|--|--|

| Package<br>Description         | Number<br>of Pins<br>(N) | Maximum<br>Length<br>(L) | Maximum Width<br>Without Leads<br>(B) | Maximum Width<br>Including Leads<br>(W) | Maximum Height<br>Above Board<br>(H) |  |  |

| SOJ (Small<br>Outline, J-Lead) | 20                       | 12.95                    | 7.62                                  | 8.81                                    | 3.18                                 |  |  |

# **Ordering Information**

| Device Code | Package    | Temperature      | Comcode   |

|-------------|------------|------------------|-----------|

| T - 7503 EL | 20-Pin SOJ | –40 °C to +85 °C | 107648925 |

# Notes

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET:

http://www.lucent.com/micro

E-MAIL:

docmaster@micro.lucent.com

U.S.A.:

Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA PACIFIC:

Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

Tel. (65) 778 8833, FAX (65) 777 7495

JAPAN:

Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700

EUROPE:

Data Requests: MICROELECTRONICS GROUP DATALINE: Tel. (44) 1189 324 299, FAX (44) 1189 328 148

Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Bracknell),

FRANCE: (33) 1 41 45 77 00 (Paris), SWEDEN: (46) 8 600 7070 (Stockholm), FINLAND: (358) 9 4354 2800 (Helsinki),

ITALY: (39) 2 6601 1800 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

$\begin{array}{l} Copyright @ 1998 \ Lucent \ Technologies \ Inc. \\ All \ Rights \ Reserved \end{array}$

microelectronics group